|

2.3 RISC-V与ARM和X86指令集具有的优势2.3.1 完全开源 做为开源的 ISA,RISC-V 是由 UC Berkeley 所发展的,RISC-V 正试着挑战现行主流的指令集架构。藉由 RISC-V,UC Berkeley 正试着从头打造一个全新的生态系,并将其开放,让所有人都可以使用。 对指令集使用,RISC-V 基金会不收取高额的授权费。开源采用宽松的 BSD 协议,企业完全自由免费使用,同时也容许企业添加自有指令集拓展而不必开放共享以实现差异化发展。 2.3.2 架构简单从官网上的文件可以知道,RISC-V 只有大约 100 个 Instructions,且不会再增加。如此便不需为了新增指令而增加新的电路,增加芯片的面积。此外,RISC-V 提供 16、32、64bits 等多种内存定址方式,让厂商有更多的选择。

RISC-V 架构秉承简单的设计哲学。体现为:在处理器领域,主流的架构为 x86 与 ARM 架构。x86 与 ARM 架构的发展的过程也伴随了现代处理器架构技术的不断发展成熟,但作为商用的架构,为了能够保持架构的向后兼容性,其不得不保留许多过时的定义,导致其指令数目多,指令冗余严重,文档数量庞大,所以要在这些架构上开发新的操作系统或者直接开发应用门槛很高。而 RISC-V 架构则能完全抛弃包袱,借助计算机体系结构经过多年的发展已经成为比较成熟的技术的优势,从轻上路。RISC-V 基础指令集则只有 40 多条,加上其他的模块化扩展指令总共几十条指令。 RISC-V 的规范文档仅有 145 页,而“特权架构文档”的篇幅也仅为 91 页。 2.3.2 易于移植现代操作系统都做了特权级指令和用户级指令的分离,特权指令只能操作系统调用,而用户级指令才能在用户模式调用,保障操作系统的稳定。RISC-V提供了特权级指令和用户级指令,同时提供了详细的RISC-V特权级指令规范和RISC-V用户级指令规范的详细信息,使开发者能非常方便的移植linux和unix系统到RISC-V平台。 2.3.4模块化设计模块化的方式组织在一起,从而试图通过一套统一的架构满足各种不同的应用场景。用户能够灵活选择不同的模块组合,来实现自己定制化设备的需要,比如针对于小面积低功耗嵌入式场景,用户可以选择 RV32IC 组合的指令集,仅使用 Machine Mode(机器模式);而高性能应用操作系统场景则可以选择譬如 RV32IMFDC 的指令集,使用 Machine Mode(机器模式)与 User Mode(用户模式)两种模式。 2.3.5完整的工具链在软件支持方面,因为 RISC-V 是全新的指令集架构,因此现行的软件都要做修整方能配合使用。为了做后续的发展,他们已经为 RISC-V 开发出 GCC / glibc / GDB、LLVM / Clang、Linux、Yocto、Verification Suite 等软件。

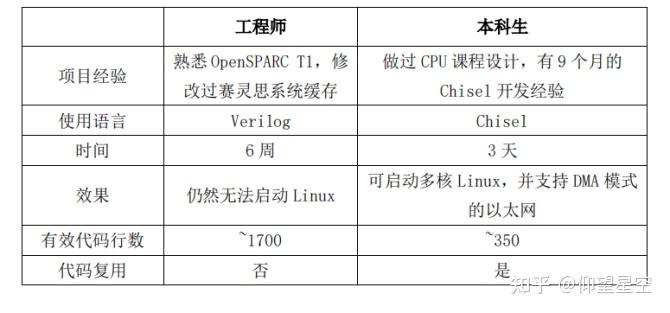

在硬件开发工具部分,他们设计出全新的硬件描述语言 Chisel,以 Scala 为语言核心,辅以硬件开发工具,可以将 Scala 所开发出的电路轻易地转换成 C++ 的电路模拟,或者 FPGA、ASIC 用的 Verilog Code,并进行合成和绕线,提升硬件设计的效率。 在 2012 年的DAC会议上发表了一门新的编程语言Chisel来进行硬件的敏捷开发。Chisel的主要目标是减少项目中的重复代码,提高代码密度,从而提升开发效率、代码可读性和易维护性。编写 Chisel 代码后,用 Chisel 编译器将其编译成底层的Verilog 代码(网表),可用于标准的 ASIC 和 FPGA 流程。虽然Chisel 支持传统硬件描述语言不具备的很多高级特性,但 Chisel 还是一门硬件构建语言,而不是高层次综合语言。硬件构建语言用于描述电路具体如何构建,而高层次综合语言则用于描述算法的流程。表 9 中总结了 Chisel 和传统的硬件描述语言(Verilog 和 SystemVerilog)之间的对比。  相关调查表明,Chisel 比 Verilog 编码效率高,下图为二级缓存开发案例对比  下图为Chisel 和 Verilog 的性能、功耗、面积和对比  2.3.6 性能堪比部分ARM 2.3.6 性能堪比部分ARM为了证明 RISC-V 的实际效能,UC Berkeley 甚至实际设计出一颗芯片,并将其制作出来。为了确保公平性,选用和 ARM Cortex-A5 相同的台积电制程。采用 RISC-V 的 CPU 不但面积比较小,运算速度较快,而且还耗较少的电。足以证明 RISC-V 做为新进者,已经具有挑战 ARM 的潜力。 2.3.7在芯片设计方面与ARM和X86对比 2.4 RISC-V面临的挑战2.4.1 碎片化的风险 2.4 RISC-V面临的挑战2.4.1 碎片化的风险首先RISC-V架构开源规则本身有一定的局限性。RISC-V强调完全开源的设计,并且让取用者可任意加上专属指令集,甚至可以自由选择将架构封闭还是维持开源。这样就导致了RISC-V架构可能出现,虽然拥有更多的指令集,却无法共用的问题。 当各个公司做出具有本身公司特色的芯片时,如果他们选择将自己的专属指令集保密,那么若干年后,很可能出现芯片互不兼容的情况,而这样的碎片化问题往往是不利于产业发展的。 例如Android系统本身是一个开源的系统,但经过华为、小米、OPPO等厂商各自开发成自己的系统之后,就变得不再互相兼容,这也是RISC-V架构开源规则本身的局限性。 2.4.2 生态建设尚不完整与X86和ARM架构相比,RISC-V架构生态欠缺,导致目前无法抢占市场,英特尔推动的x86架构市场依旧庞大,几乎从传统PC 到数据中心规模的服务器都在使用基于x86架构的处理器,同时相关软件带动的应用服务也有长达40年的优化发展历史。 对于ARM架构已产生的庞大市场应用规模,RISC-V架构更加难以取代,而且ARM的IP授权模式已经趋于完善,尽管授权费用高昂,但各大厂商依旧使用,例如我国华为海思、展讯、中兴、全志等芯片皆是采用ARM架构。 2.4.3 需要进一步进行技术验证开放指令集与开源芯片的稳定性及成熟度还需要通过硅验证及大量的 市场应用来进行检验,目前国内流片成功的案例较少。

|